Diseño del esquema

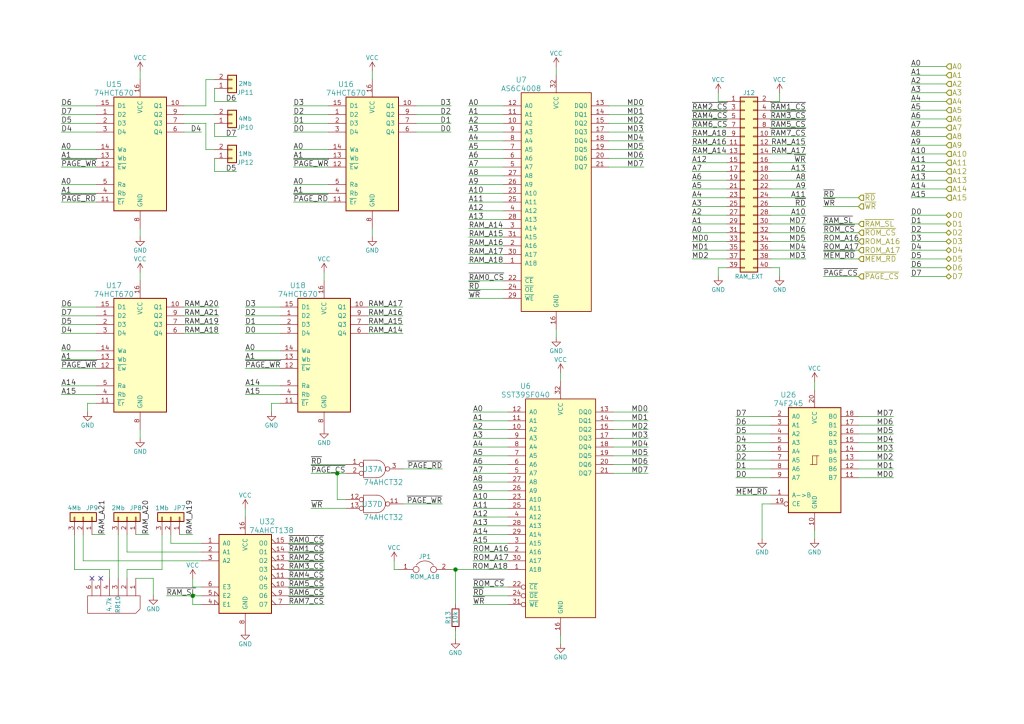

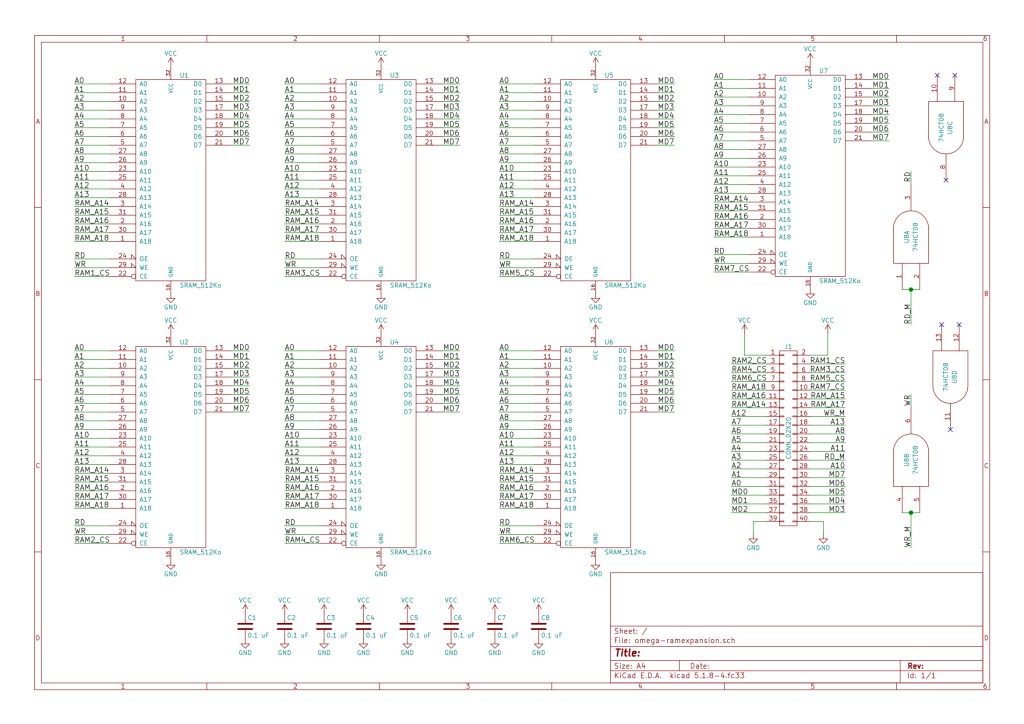

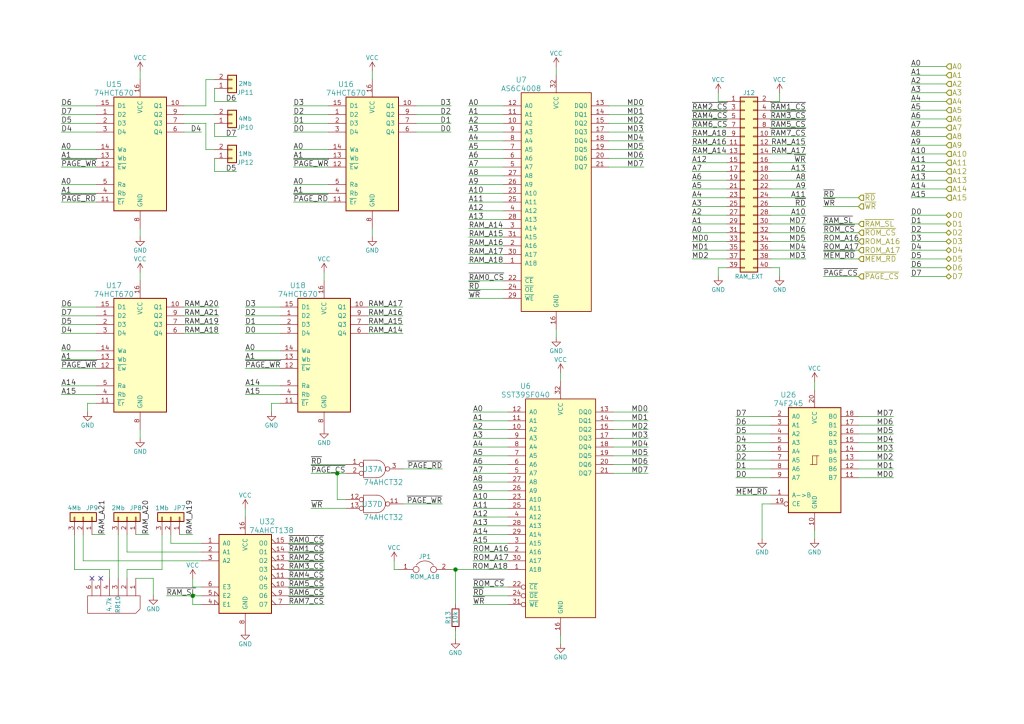

El esquema del o4Mega es muy básico, principalmente por que no se trata de un expansor de RAM en sí, si no de de una placa que conecta los chips de RAM a la placa base. Tiene 7 chips conectados todos como se muestra en la imagen a continuación y la única diferencia es que cada uno tiene su señal /RAM?_CS independiente:

Supongo que todo aquel que conozca un mapeador para la norma MSX habrá podido comprobar que en este circuito no lo es, aquí solo están los chips de RAM pero falta el registro que guarda la posición de memoria a mostrar y la lógica de selección de memorias.

El puerto J12 del OMEGA incluye las líneas que forman el BUS de datos, el BUS de direcciones, y además tiene una señal de /RD (read) y /WR (write) para indicar a las memorias cuando está leyendo o escribiendo, todo esto siempre es necesario para dirigirse a posiciones de memoria. Pero además tiene una señal de «chip select» por cada chip de la placa (por ejemplo /RAM1_CS). Esta señal indica a que chip de destino se está dirigiendo el procesador en cada momento.

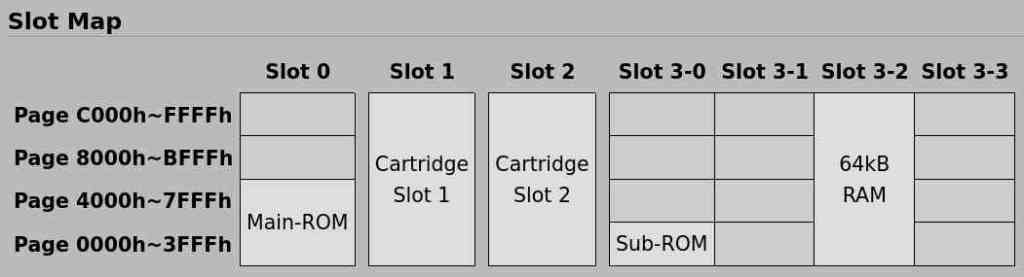

Este es un esquema de memoria común en la mayoría de MSX2 está basado en el sistema de SLOTS y SUBSLOTS que todos conocéis:

Pero el Z80 (cpu) solo puede dirigirse en realidad a 64K de memoria en cada momento, y en todo caso, nunca más allá de 1M aun desplegando todos los SLOTS en SUBSLOTS, mientras que un expansor de RAM puede llegar a 4Mb.

Esto es debido a que en realidad el mapeador de RAM es independiente del sistema de SLOTS. Tiene un circuito dedicado a conectar 4 bloques de 16K de la RAM con las 4 páginas de un SLOT o SUBSLOT. Por ello su único limite es el total de memoria que puede direccionar, que son 16K por bloque multiplicados por 256 posiciones posibles, esto da una capacidad total de 4096K (4Mb).

El circuito mapeador del OMEGA está en realidad en su placa base y no en el o4Mega como cabría pensar.

Aun sin el módulo de ampliación o4Mega, el OMEGA es capaz de acceder a 512K integrados en la placa base, precisamente gracias a que el mapeador ya está incorporado en la placa principal.

Por tanto, es la placa base quien selecciona que chip debe activarse para cada zona de memoria a utilizar mediante las antes mencionadas líneas /RAM1_CS – /RAM7_CS. Este es el circuito de memoria del Omega y en él está incluido el mapeador:

Todo empieza con la señal …

… que escribiré en adelante como /PAGE_CS o «PAGE_CS negada«.

Para quien no lo sepa:

| Las señales de un circuito tienen un nombre que identifica su utilidad y a veces ese nombre lleva una raya encima. Esto significa que es una señal «negada», o invertida. Cuando sucede en una ecuación significa que hay que invertir su resultado, pero cuando es propiamente la etiqueta de la señal en el esquema (como es el caso) significa que lo que dice la etiqueta es cierto cuando su valor es «0» y falso cuando es «1». Ejemplo: Una señal llamada «/enciende_LED» significa que el led estará encendido cuando el valor de esta conexión sea «0» y apagado cuando sea «1». Las señales que no llevan esa barra son ciertas cuando su valor lógico es «1». En el ejemplo anterior la etiqueta se llamaría «apaga_LED», porque describe que la señal está a «1» (cierto) cuando el LED está apagado. |

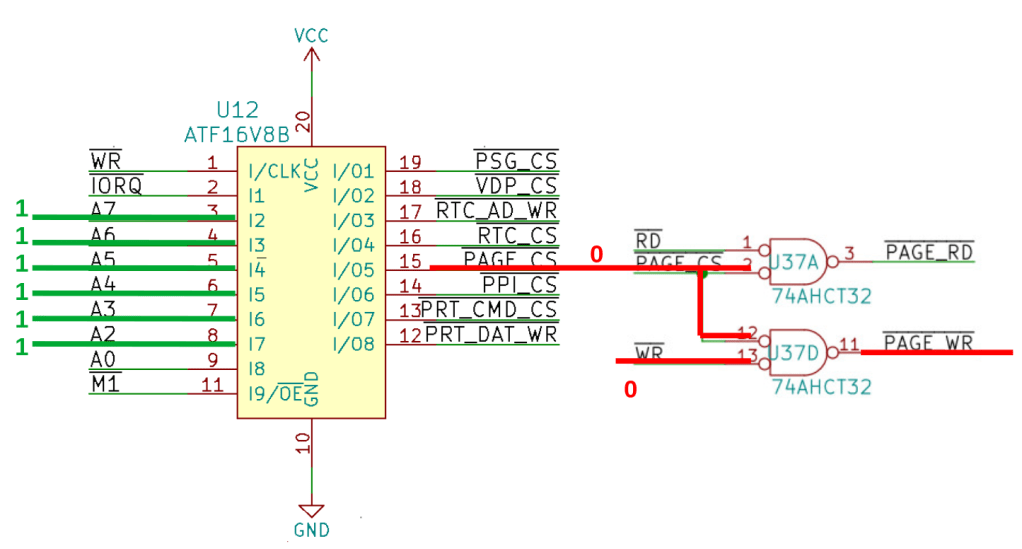

Como decía todo empieza con /PAGE_CS que es una señal generada desde U12. U12 es el GAL «selector de chips», su código se encarga de activar los diversos chips que están conectados a un puerto E/S. Si el CPU se dirige a uno de esos puertos, U12 activa la señal «chip select» del chip que lo controla.

En este caso /PAGE_CS se activa con una llamada a los puertos hexadecimales FC, FD, FE y FF (en adelante FCh, FDh, FEh y FFh).

Como no hay un único chip que sea en sí el mapeador, /PAGE_CS actúa sobre un circuito que cumple esa función, empezando por:

Aquí se combina la señal de /PAGE_CS con /RD (lectura) y /WR (escritura) de tal forma que se transforma en /PAGE_RD que activa la lectura de los registros del mapeador y /PAGE_WR que activa la escritura en dichos registros.

| Un «registro» es como una posición de memoria de un byte. Diversos chips tienen uno o varios registros internos y sirven para transferir ordenes, comunicar estados o intercambiar datos. También hay registros dentro de la propia Z80, o incluso circuitos formados por varios chips que guardan la información de un registro. |

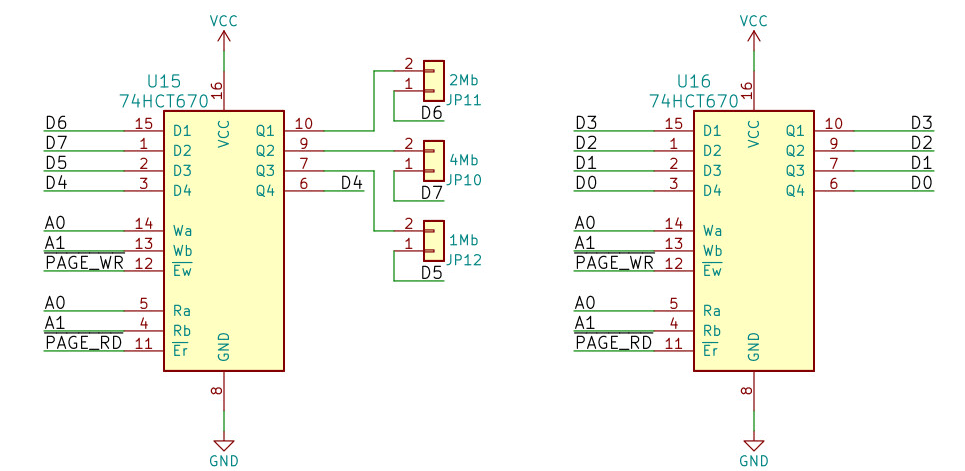

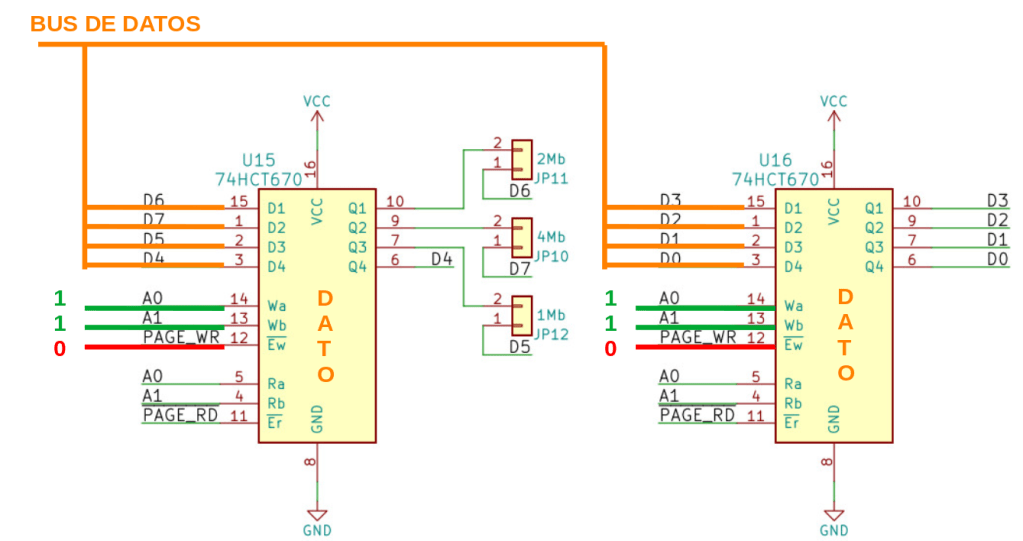

Las señales /PAGE_RD y /PAGE_WR actúan directamente sobre los 4 chips 74HC670 de la placa base, comencemos viendo U15 y U16, este es el esquema:

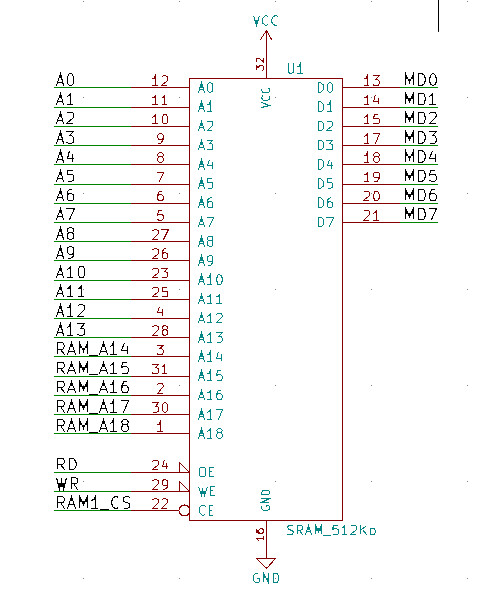

Los 74HC670 son chips de almacenado y lectura de 4×4 bits y permiten acceso de lectura y escritura simultaneo. A menudo se utilizan por parejas para conseguir el almacenamiento y lectura de 4 bytes. En este caso U15 se encarga de la mitad alta del dato (byte) y U16 de la mitad baja, así que entre los dos son 4 registros de 1 byte.

Cuando el Z80 escribe en los puertos FCh-FFh la señal /PAGE_WR cambia de estado (pasa a «0») y habilita la escritura en estos chips (el pin etiquetado como /Ew que significa enable write) en uno de los 4 registros internos ¿en cual? esto se selecciona mediante los pines Wa y Wb que están conectados a A0 y A1.

Si estamos escribiendo en el puerto FCh el bus de direcciones contiene «FC» en hexadecimal, es decir «11111100» en binario, por tanto A0 y A1 están a «0», de modo que el dato, en el bus de datos en ese momento, será almacenado en el registro 00 de U15+U16.

Si el dato se lee, significa que /PAGE_WR será falso y /PAGE_RD verdadero (read y write nunca están activos a la vez). El dato U15+U16 se deposita en los pines Q1 a Q4. Para que el o4Mega alcance su total capacidad los jumpers JP10 a JP12* deben estar todos conectados así que vamos a suponer que es así.

nota *: En la versión 1.2 de la placa base no existen dichos jumpers (consulte cambios en el mapeador para ver más sobre esta diferencia).

El resultado es que cuando se lee de estos chips el valor del registro vuelve al bus de datos (D0 a D7).

Por tanto, todo este montaje solo sirve para almacenar 4 bytes sin utilizar los chips de memoria.

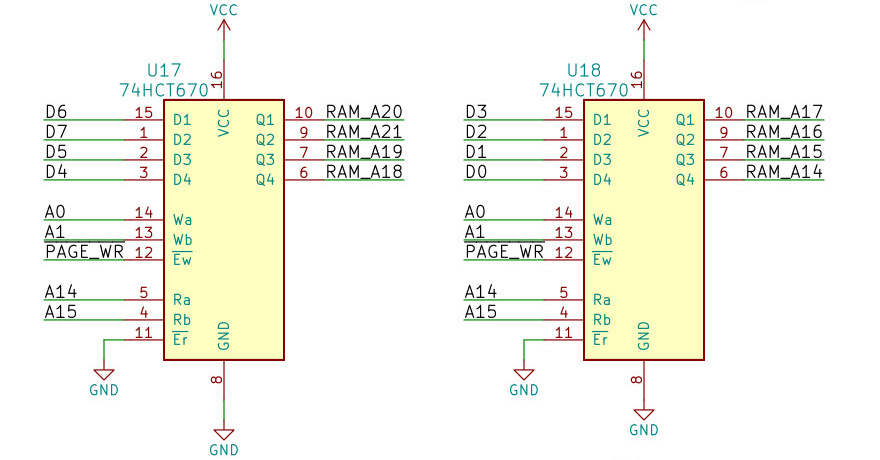

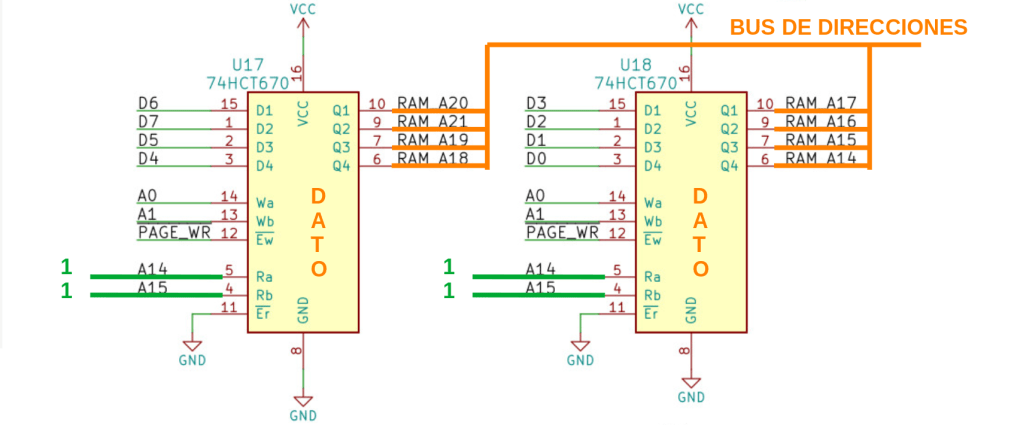

A continuación vamos a fijarnos en otra parte del circuito mapeador casi idéntica, U17 y U18:

En este caso los chips son del mismo tipo y las conexiones de entrada (escritura) son las mismas también, pero los pines de salida (lectura) están aislados del circuito anterior y generan señales nuevas, etiquetadas como RAM_A14, 15, 16… hasta RAM_A20, vamos a ver porqué.

Antes de nada decir que, como para escritura es idéntico, el contenido de los registros dentro de U17 y U15 será idéntico y también el contenido de U18 y U16, por lo que las dos parejas de chips guardan la información por duplicado.

En cuanto a la lectura, dado que las salidas Q1-Q4 no están conectadas con las líneas de entrada, la línea /Er puede estar habilitada siempre y en efecto /Er está conectada permanentemente a GND. Así que la salida siempre está mostrando el contenido de alguno de los registros.

¿Y cual es el registro seleccionado? El registro se selecciona utilizando Ra y Rb conectado a las señales A14 y A15. Volvamos a ver esta imagen:

Esta imagen muestra las páginas de un SLOT del sistema MSX. Bien, pues si expresamos en binario estos números (0000h, 4000h, 8000h y C000h) veremos que son idénticos salvo por los 2 bits de la izquierda, es decir A14 y A15.

| hexa | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| 0000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 4000 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 8000 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| C000 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Por tanto, cuando la dirección de memoria actual para el Z80 está en la página 0 (0000h-3FFFh) estos 2 bits contienen «00» y seleccionan el registro 00 de U17 y U18, cuando la dirección es de la página 1 contienen «01», cuando es de la página 2 contienen «10» y cuando es de la página 3 contienen «11».

El resultado de todo esto es que cuando alguien envía un dato a FCh está grabando en el registro 0 del mapeador dicho dato, y el dato que esté grabando será la dirección del bloque conectado a la página 0 (en el SLOT del mapeador). Lo mismo sucede al grabar en FDh con el registro 1 y la página 1, con FEh y la página 2 y con FFh y la página 3.

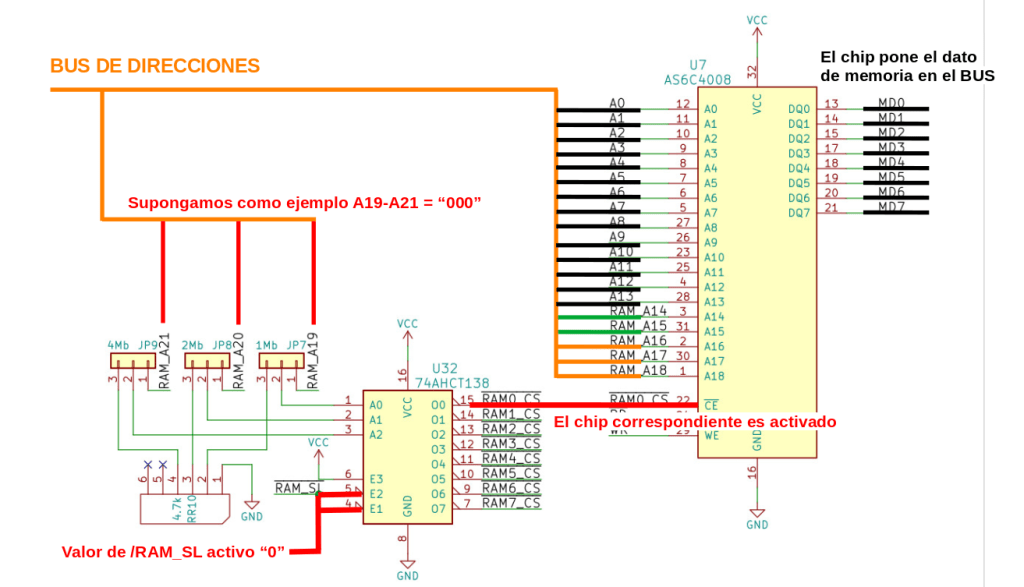

Bueno, ya parece que lo tenemos casi todo, aunque aun falta esta parte del circuito:

Para que el o4Mega alcance su total capacidad los jumpers JP7 a JP9* deben estar todos conectados en la posición 1-2, así que vamos a suponer que es así.

nota *: En la versión 1.2 de la placa base no existen dichos jumpers (consulte cambios en el mapeador para ver más sobre esta diferencia).

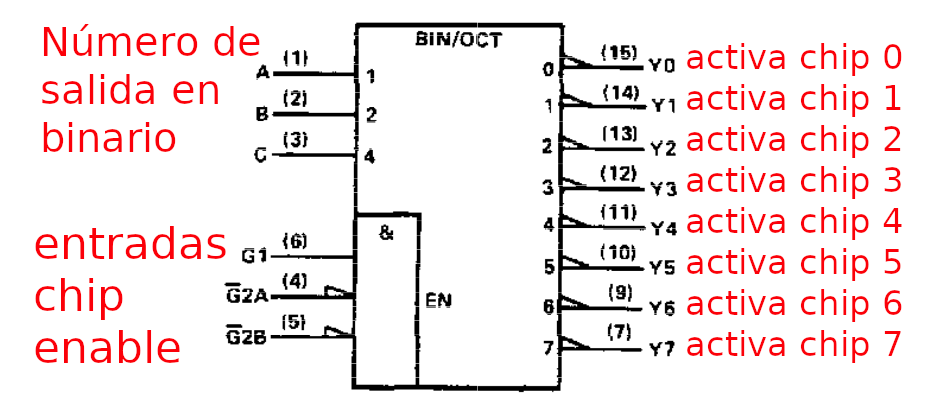

El 74AHCT138 (U32) es un decodificador o multiplexor de 3 a 8 líneas. transforma un número binario en su entrada de 3 bits (A0, A1 y A2) en una activación independiente en una de sus salidas, de modo que cuando en A0-A2 hay el número «0» se activa el pin llamado «00» y sólo ese. Si el número en la entrada es 3 (011) se activa el pin 03, etc, etc.

Estos pines de entrada están conectados a las líneas de dirección A19, A20 y A21 que son las líneas de dirección por encima de 512K, es decir, más allá de la capacidad de ninguno de los chips en el OMEGA.

Cada combinación de números formados por esos 3 bits identifica uno de los segmentos de 512k en los que se divide la RAM del mapeador, por tanto cada número diferente a la entrada identifica un chip de RAM diferente y hay una salida independiente para cada chip de RAM.

Como se puede ver en la figura, este chip tiene además 3 entradas para habilitar/deshabilitar la salida. Tal como se ve en el esquema (más arriba) la activación depende básicamente de la señal /RAM_SL.

/RAM_SL es una señal generada en el chip GAL llamado «slot select» (U13). Esta señal se activa cuando está seleccionado el SLOT del mapeador de RAM (3-2). Así que cuando el sistema conecta cualquier página de ese SLOT a la memoria mapeada, U32 habilita su salida y el chip de RAM que contiene ese bloque es seleccionado.

Por último vamos a mencionar el resto de elementos en el circuito de memoria del OMEGA:

- J12 es simplemente un conector de pines que transmite las señales hasta el conector J1 del módulo o4Mega.

- U7 es una memoria RAM de 512K exactamente igual a las incluidas en el o4Mega, sólo que está en la placa base. Es la memoria RAM principal del sistema y por ello está controlada por la señal /RAM0_CS.

- U26 es un buffer.

Un buffer es chip que sirve para mantener los niveles de tensión de las señales digitales, algo como copiar la entrada en la salida. Este tipo concreto tiene además un pin que controla el sentido de la comunicación. Por lo que U26 copia el contenido de sus pines A0-A7 en B0-B7 cuando A->B es cierto («1») y a la inversa cuando ese pin es falso.

- U6 es una memoria FLASH-ROM de 512K. Debido a que el OMEGA tan solo necesita 256K, el contenido de la ROM está dividido en dos segmentos que se seleccionan mediante el jumper JP1, lo que permite seleccionar que contenido ROM queremos al arranque del sistema.

Aunque ROM quiere decir memoria de sólo lectura, este chip es una memoria FLASH, lo que permitiría reescribir su contenido, y de hecho su pin de escritura está conectado al resto del circuito. De hecho existe un programa diseñado para actualizar la memoria ROM «flash» del omega, en: https://github.com/lfantoniosi/oflash gracias al usuario retrocanada76.

un ejemplo de funcionamiento:

El Z80 envía un número al puerto FFh para modificar el banco de RAM conectado a la página 3. Por tanto los bits A7-A2 se activan («1») y la línea /WR también («0»). A continuación U12 activa /PAGE_CS cosa que mediante U37 se convierte en /PAGE_WR activo («0»):

Con la línea /PAGE_WR activa y las líneas A0 y A1 ambas a «1» el registro 3 del mapeador se graba con la información que contenga el bus de datos, fijando así cual será el banco de RAM mapeado en la página 3.

Cuando el Z80 consulta la página de memoria número 3, A14 y A15 son igual a «1» y por tanto U17 y U18 devuelven el dato contenido en el registro 3 del mapeador al bus de direcciones, de A14 a A21:

El Bus de direcciones tiene ahora la información que selecciona un chip (A19-A21) y un banco de memoria (A14-A18). La dirección se completa con el resto de líneas del Bus de datos (A0-A13) provenientes directamente del Z80 y devuelven el dato de dicha posición de memoria en el bus de datos.

Las líneas a «0» están pintadas en rojo, las que están en «1» en verde y aquellas cuyo dato se desconoce en naranja (datos del mapeador) y negro (datos cualesquiera).

Para simplificar el ejemplo he supuesto que el valor de bits A19 a A21 era «0» y así poder mostrar cual sería el chip de RAM seleccionado (U7 de la placa base).

Jordi Solís MSXmakers member.